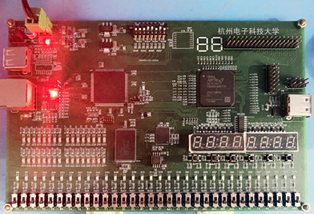

HDU-XL-01计算机组成与体系结构实验箱,新一代基于FPGA的教学实验设备,能够支持开展《数字电路设计》、《计算机组成原理》、《计算机系统结构》、《接口与通讯》等课程实验教学,以及基于FPGA的学生竞赛和学生科研等。计算机组成与体系结构实验箱包括本地实验系统和远程实验系统,本地实验系统包括本地FPGA实验板卡和本地烧录软件;远程实验系统包括远程FPGA实验板卡和远程实验软件平台。本地实验系统和远程实验系统可以分别单独使用。

一、计算机组成与体系结构实验箱的特点

1.完整丰富的硬件课程实验教学内容,确保实验室建设的先进性

HDU-XL-01实验系统主芯片采用Xilinx Artix-7系列芯片,软件开发平台为当前商业主流的Xilinx Vivado Design Suite或Xilinx ISE Design Suite。在实验项目设计上,注重基于系统化教学概念的解决复杂工程能力培养,注重知识的基础性、完整性和课程衔接性,设计难度上遵循“用简单方式学习最基本的原理”,适合面向大众化教育的地方高校教学。

《数字电路设计》实验分3个层次:第一个层次侧重组成计算机各部件的“芯片级”硬件原理,通过15个实验夯实基础;第二、三层次设计了定时与分频、自动售货机等实验,侧重数字电路基础知识的灵活运用。《计算机组成原理》实验围绕主流MIPS模型机的结构,提供了运算器、控制器、存储器、控制器等各部件的设计性教学实验内容,特别是提供了获得2019年全国实验案例竞赛一等奖的具有中断处理功能的单周期MIPS CP模型机设计和多周期MIPS CPU模型机设计,以及理想流水线实验等,可培养学生对计算机组成结构和工作原理具有全面清晰的认识。

2.远程实验系统的特点

1)突破实验室开放时间和空间限制,支持“随时随在”的实验;

2)远程实物实验,远端并非虚拟板卡,而是真实的FPGA板卡;

3)通过预约和定时回收技术,确保用户在预约时间内独占式使用远端实物板卡,同时又避免了资源浪费;

4)网页方式访问,用户无需安装任何终端程序;

5)实验过程中支持交互式操作,回传数据有采样信号和视频信号两种,高效、准确、实时;

6)完全兼容本地板结构和程序。

3.技术参数

板块能够同时支持烧录和运行调试在ISE和vivado两种平台上编写和综合生成的bit文件;

主芯片采用Xilinx Artix-7系列FPGA芯片,开发板为6层线路板。

结构参数如下:

1)主FPGA芯片:

Xilinx Artix-7系列的XC7A100TTM FGG484BX1719。XC7A100T FGG484有101440个逻辑单元,采用28纳米工艺,能提供多达300个可使用I/O,I/O资源分为6个Bank,每个可以接不同的供电电压。

2)具有272M存储器:

128M Micron公司的Cellular RAM;

16M SPANSION公司的并行FLASH;

128M WINBOND公司的Quad-mode SPI串行FLASH;

3)使用100MHz晶振;

4)提供丰富的外设接口:

10/100M Ethernet以太网接口;

USB-UART接口;

A型USB接口(USB-HID),可以接鼠标、键盘和记忆棒;

1个USB接口,提供电源、程序烧录和数据传输;

5)提供通用I/O设备(GPIO):

32个拨码开关输入;

本地板卡8个(远程板卡6个)经硬件消抖的按键;

8个7段数码管(循环扫描方式访问);

32个LED显示灯。

6)具备远程实验调试扩展功能:

注:本地板卡重新烧录固件可支持远程访问(限6个按钮)。远程板卡重新烧录固件可支持本地调试;

具备远程程序下载和调试的扩展功能;

可以实现远程的状态设定和采集扩展功能;

具备远程拍照观测的扩展功能;

无需改动,在同一块板子上就可扩展为远程虚拟仿真实验板

与远程虚拟仿真实验平台兼容

4.结构特点:

1)板卡上FPGA芯片通过两种方法实现配置:

在PC机上,使用配置软件,通过USB PROG口(P2)在线配置FPGA;

通过JTAG口(P6)在线进行配置;

2)三种板卡供电方式:

USB口供电;

外部电源和网络端口供电;

通过跳线(P13)选择供电。

3)板卡片外有三种存储器:

16MB的Cellular Ram(Micron M45W8MW16);

16MB的并行FLASH S29AL016J;

16MB的串行FLASH 支持Quad-mode,Dual-mode和标准的SPI总线传输协议,总线速率达到50MHz。

4)两个USB接口:

1个Micro USB接口(P2),编程、传输数据和供电都可以通过这个接口完成,该USB编程接口位于板卡的左上角,实验时,用户需用连接线将该USB口与PC机连接起来,从而实现板卡供电和数据通信。

1个Micro USB接口(P8),可以用来与PC机进行串口通信。

5)I/O 设备特点:

8个按键都经过了硬件消抖处理;

8个7段数码管,经3-8译码器译码控制,采用循环扫描方式进行访问。

5.硬件保护措施降低实验设备损坏率

1)USB供电插拔加固,有效防止暴力操作带来的电源损坏;

2)两面喷三防漆保护,双层有机玻璃保护,有效防止精密元器件被直接触摸造成的损坏;

3)铜柱支架有效防止板卡变形损坏;

6.其他服务

提供《计算机组成原理》和《数字电路设计》两门课程的全套实验资源包;免费提供实验资源包的升级

可选配用于辅助教学和出题的软件,如编程驱动的交互式模型机虚拟仿真教学软件、富含趣味性的游戏版模型机虚拟仿真教学软件、机器数运算与转换虚拟仿真软件。

三、主要实验内容

1.支持《数字电路设计》实验

1)基本实验项目

实验1 五输入表决器设计

实验2 多路数据选择器设计

实验3 译码器设计

实验4 二进制优先级编码器设计

实验5 数值比较器设计

实验6 加法器设计

实验7 加/减法运算器设计

实验8 基本RS触发器设计

实验9 D触发器设计

实验10 JK 触发器设计

实验11 同步二进制计数器设计

实验12 十进制计数器设计

实验13 可逆计数器设计

实验14 基本寄存器设计

实验15 移位寄存器设计

2)扩展实验项目

实验16 定时与分频实验

实验17 流水灯实验

实验18 数码管扫描显示

实验19 数字钟设计

实验20 小键盘扫描实验

实验21 串口通信实验

3)综合实验项目

实验22 寄存器堆设计

实验23 按键消抖与单脉冲产生实验

实验24 出租车计费器设计

实验25 交通灯设计

实验26 自动售货机设计

2. 支持《计算机组成原理》实验:

实验1 平台使用和HDU-XL-01实验板卡测试实验

实验2 全加器设计实验

实验3 超前进位加法器设计实验

实验4 乘法器设计实验

实验5 除法器设计实验

实验6 多功能ALU运算器设计实验

实验7 寄存器堆设计实验

实验8 存储器设计实验

实验9 MIPS汇编器与模拟器实验

实验10 取指令与指令译码实验

实验11 实现R型指令的CPU设计实验

实验12 实现R-I型指令的CPU设计实验

实验13 实现R-I-J型指令的CPU设计实验

实验14 中断控制设计实验

实验15 多周期CPU设计实验

实验16 理想流水线设计实验